|

Xilinx EDK. Diseño de aplicaciones empotradas en FPGAs con Microblaze y Power-PC |

Inicio |

Esta página está dedicada al curso "Xilinx EDK. Diseño de aplicaciones empotradas de 32 bits con Microblaze y Power-PC" que se celebra en la Universidad de Vigo.

En este curso se estudian los microprocesadores Microblaze de Xilinx y Power-PC, para su implementación mediante FPGAs de las familias Spartan y Virtex de Xilinx. Para poder trabajar con estos microprocesadores, es necesario aprender el manejo de la herramienta EDK de Xilinx.

Este es un curso de posgrado, organizado por el Departamento de Tecnología Electrónica de la Universidad de Vigo, orientado tanto a universitarios como a profesionales del sector electrónico.

En Septiembre de 2010 se ha celebrado la cuarta edición de este curso, con una aceptación muy buena entre los profesionales del sector electrónico.

Más abajo en esta misma página se encuentra la información detallada del curso.

Preinscripción: del 30 de Agosto al 4 de Septiembre de 2010 (enlace disponible sólo en estas fechas).

Matrícula: del 6 al 11 de Septiembre de 2010 una vez comunicada la admisión en el curso (enlace disponible sólo en estas fechas).

El curso se imparte completamente en castellano.

|

|

|

|

|

OBJETIVOS

- Estudio de los métodos de diseño de aplicaciones de microprocesadores empotrados de 32 bits mediante FPGAs.

- Estudio de los microprocesadores de 32 bits “Microblaze" y “Power-PC”, implementables en las FPGAs de las familias Spartan y Virtex de Xilinx.

- Aprendizaje de la herramienta EDK, necesaria para el desarrollo de aplicaciones empotradas de 32 bits mediante FPGAs de Xilinx.

- Diseño de periféricos de usuario y de su conexión a los buses de los microprocesadores empotrados de 32 bits.

- Realización de sistemas digitales de aplicación real con microprocesadores de 32 bits empotrados en FPGAs.

DESTINATARIOS

- Profesionales en el campo de la Electrónica con experiencia en microprocesadores y circuitos de lógica programable (PLDs, FPGAs), siempre y cuando reúnan los requisitos legales de acceso a la universidad.

- Titulados de las titulaciones:

- Ingeniería Técnica Industrial.

- Ingeniería Técnica de Telecomunicación.

- Ingeniería de Telecomunicación.

- Ingeniería Industrial.

- Alumnos de últimos cursos de las mismas titulaciones.

Los estudiantes de primer y segundo ciclo tendrán derecho a la cuota de matrícula reducida, siempre que acrediten dicha condición.

CONDICIONES DE ACCESO

Los solicitantes deberán poseer los siguientes conocimientos:

- Nivel básico del lenguaje VHDL.

- Manejo de la herramienta Foundation ISE de Xilinx para el diseño con FPGAs.

- Microprocesadores. Arquitectura general. Lenguaje ensamblador.

- Nivel básico de lenguaje C.

- Manejo básico del sistema operativo Windows.

CRITERIOS DE SELECCIÓN

1. Se dará prioridad a los profesionales que trabajen

actualmente en el sector electrónico. A continuación, se dará prioridad a los

profesores que impartan docencia de Electrónica, luego a los titulados en paro

y, por último a los estudiantes de la especialidad de Electrónica de cualquiera

de las titulaciones arriba mencionadas.

2. Sólo se tendrá en cuenta a los solicitantes que cumplan los requisitos

indicados en el apartado “Condiciones de acceso”.

3. En caso de conflicto, éste se resolverá en base al orden de inscripción.

CALENDARIO

25 HORAS presenciales en 5 días

lectivos consecutivos, del 13

al 17 de Septiembre de 2010.

Horario de 9:00 a 14:30, con un descanso de ½ hora.

5 horas virtuales (no presenciales)

PRECIO

Los estudiantes de primer y segundo ciclo que lo acrediten antes de realizar la matrícula tendrán derecho a la cuota de matrícula reducida de 275 €.

Los titulados universitarios deberán pagar la cuota de matrícula completa de 550 €.

PROGRAMA

MÓDULOS TEÓRICOS:

INTRODUCCIÓN AL DISEÑO DE SISTEMAS EMPOTRADOS DE 32 BITS.

1.1.- Introducción.

1.2.- Microprocesadores de 32 bits empotrables en FPGAs de Xilinx.

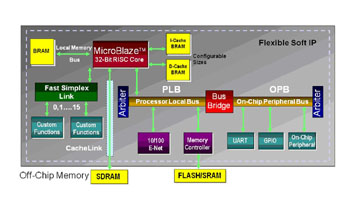

1.2.1.- Microblaze.

1.2.2.- Power PC.

1.3.- Codiseño “hardware” / “software”.

1.4.- Codiseño de Sistemas Empotrados mediante la herramienta EDK de Xilinx.

ARQUITECTURA DE LAS FPGAs DE LA FAMILIA VIRTEX DE XILINX

2.1.- Introducción.

2.2.- Arquitectura de las FPGAs de la familia Virtex de Xilinx.

2.2.1.- Recursos lógicos:

2.2.2.- Recursos de interconexión.

2.2.3.- Tecnología.

2.2.4.- Otras características.

2.2.5.- Familias afines. Características comunes con la

familia Spartan.

MICROPROCESADOR MICROBLAZE DE XILINX

3.1.- Introducción.

3.2.- Arquitectura interna del microprocesador Microblaze.

3.2.1.- Estructura del microprocesador Microblaze.

3.2.2.- Mapa de memoria.

3.2.3.- Buses del microprocesador Microblaze. PLB. OPB. FSL.

3.2.4.- Periféricos básicos. Temporizador. UART RS232.

Controlador de interrupciones.

3.2.5.- Periféricos opcionales. Unidad de coma flotante (FPU).

MICROPROCESADOR POWER-PC DE XILINX

4.1.- Introducción.

4.2.- Arquitectura interna del microprocesador Power PC.

4.2.1.- Estructura del microprocesador Power PC.

4.2.2.- Mapa de memoria.

4.2.3.- Periféricos básicos.

4.2.4.- Periféricos opcionales.

MÓDULOS PRÁCTICOS:

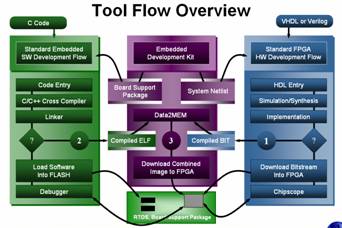

ENTORNO EDK PARA EL DISEÑO DE SISTEMAS EMPOTRADOS BASADOS EN

MICROPROCESADORES DE 32 BITS DE XILINX.

1.1.- Introducción.

1.2.- EDK. “Embedded Development Kit” de Xilinx.

1.2.1.- Flujo de codiseño.

1.2.2.- Tutor para la creación de sistemas empotrados. “Base

System Builder”.

1.2.3.- Adición de periféricos predefinidos (“IP cores”).

1.5.- Realización de ejemplos básicos de sistemas empotrados basados en el

microprocesador Microblaze.

1.6.- Realización de ejemplos básicos de sistemas empotrados basados en el

microprocesador Power PC.

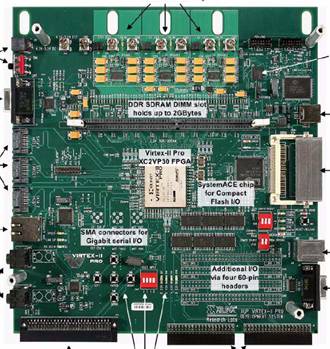

1.6.- Implementación de los sistemas desarrollados en placas de evaluación de

Digilent.

REALIZACIÓN DE CIRCUITOS PERIFÉRICOS PARA LOS MICROPROCESADORES EMPOTRADOS DE

XILINX.

2.1.- Introducción.

2.2.- Interfaz para periféricos básicos. GPIO.

2.3.- Interfaz para periféricos avanzados. IPIF.

2.4.- Desarrollo de periféricos de usuario (“Custom IP”).

Controlador de visualizador LCD.

2.5.- Desarrollo de coprocesadores de usuario.

Filtro FIR.

Conversor de color RGB a tonos de

gris.

ENTORNO SDK PARA EL DISEÑO DE SOFTWARE DE MICROPROCESADORES DE 32 BITS DE

XILINX.

3.1.- Introducción.

3.2.- SDK. “Software Development Kit” de Xilinx.

3.2.1.- Herramientas GNU (GCC, ASsembler).

3.2.2.- Editor. Compilador. Enlazador (“linker”).

3.2.3.- Bibliotecas suministradas.

3.2.4.- Analizador de prestaciones (“software profiler”).

3.3.- Realización de ejemplos.

3.3.1.- Temporizador acoplado por interrupción.

VERIFICACIÓN HARDWARE/SOFTWARE DE APLICACIONES EMPOTRADAS.

4.1.- Introducción.

4.2.- Simulación de los sistemas empotrados mediante Modelsim.

4.3.- Depuración de los sistemas empotrados mediante el depurador XMD desde EDK.

4.4.- Depuración de los sistemas empotrados mediante el depurador “GNU debugger”

desde SDK.

4.5.- Co-verificación HW/SW de los sistemas empotrados mediante el analizador

hardware “Chipscope” de Xilinx y el depurador software “GNU debugger”.

DESARROLLO DE APLICACIONES COMERCIALES BASADAS EN MICROPROCESADORES

EMPOTRADOS DE 32 BITS DE XILINX.

5.1.- Introducción.

5.2.- Utilización de memorias externas para el almacenamiento de la

configuración del sistema empotrado.

5.3.- Utilización de memorias externas para el almacenamiento de los programas.

5.4.- Carga de los programas al finalizar la configuración. Programas “Bootloader”.

5.5.- Definición de placas de desarrollo (“Board Support Package”).

5.6.- Integración de un microprocesador empotrado en un diseño más complejo a

través de la herramienta Foundation ISE.

5.7.- Aplicaciones comerciales.

TRABAJOS DE DISEÑO DE APLICACIONES BASADAS EN

MICROPROCESADORES EMPOTRADOS DE 32 BITS DE XILINX.

6.1.- Realización de la aplicación asignada.

EVALUACIÓN

- Asistencia a las horas presenciales del curso obligatoria. Es necesario asistir al menos al 80% de las horas presenciales para obtener el diploma del curso.

- Realización correcta de los trabajos de diseño de sistemas digitales basados en microprocesadores de 32 bits implementados en FPGAs de Xilinx.

Una vez considerados APTOS, a los alumnos/as se les expedirá el diploma de CURSO DE FORMACIÓN EN XILINX EDK.DISEÑO DE APLICACIONES EMPOTRADAS CON MICROBLAZE Y POWER-PC.

PROFESORADO

D. Francisco Poza González. Dr. Ingeniero Industrial. Profesor Titular de la E.T.S.I.I. de Vigo.

Tlfo: 986-812170. Email: http://www.dte.uvigo.es/profesor.php

D. Luis Jacobo Álvarez Ruiz de Ojeda. Dr. Ingeniero Industrial. Profesor Titular de la E.T.S.I.T. de Vigo.

Tlfo: 986-812090. Email: http://www.dte.uvigo.es/profesor.php

ADMINISTRACIÓN

Departamento de Tecnología Electrónica

Tlfo: 986-812163. Email: dte@uvigo.es

LUGAR

El curso tendrá lugar en el laboratorio de Sensores y Lógica Programable de la Escuela Técnica Superior de Ingenieros Industriales de Vigo, situada en el Campus Lagoas-Marcosende, en Vigo, España.

HotelesTransporte urbano a la Universidad. Las líneas U1 (Pza. América - Universidad) y U2 (Pza. España - Universidad) llegan al Campus desde dos sitios muy céntricos de Vigo, la plaza de América (o plaza de Traviesas) y la plaza de España.

Localización del laboratorio en la E.T.S. de Ingenieros Industriales

COLABORAN

Departamento de Tecnología Electrónica de la Universidad de Vigo

E.T.S. Ingenieros Industriales de Vigo

E.T.S. Ingenieros de Telecomunicación de Vigo

Silica España

Si tiene interés en este curso o desea hacernos alguna pregunta adicional de ámbito académico, puede enviarnos un correo electrónico.